检查电路板

设计规则检查

设计规则检查器用于验证 PCB 是否符合 “电路板设置” 对话框中建立的所有要求,以及所有焊盘是否按照网表或原理图连接。 KiCad 可以在布线时自动防止一些违反设计规则的行为,但许多其他的行为是无法自动防止的。 这意味着在为 PCB 生成制造文件之前,必须使用设计规则检查器。

要使用设计规则检查器,请点击顶部工具栏的 ![]() 图标,或从 检查 菜单中选择 设计规则检查器。

图标,或从 检查 菜单中选择 设计规则检查器。

DRC 控制窗口的顶部部分包含一些控制设计规则检查器的选项:

重新敷铜后再执行 DRC: 启用后,每次运行设计规则检查器时都会重新敷铜。 如果未手动重新敷铜,禁用此选项可能会导致错误的 DRC 结果。

报告每个布线的所有错误: 启用后,将报告每个布线的所有间隙错误。 禁用时,将只报告第一个错误。 启用此选项将导致设计规则检查器运行速度变慢。

测试 PCB 和原理图之间的一致性(parity): 启用后,设计规则检查器除了测试 PCB 设计规则外,还将测试原理图和 PCB 之间的差异。 在独立模式下运行 PCB 编辑器时,该选项不起作用。

运行 DRC 后,任何违规行为都会显示在 “DRC 控制” 窗口的中间部分。 违反规则、未连接的项目以及原理图和 PCB 之间的差异会显示在三个不同的标签中。 违规列表下面的控件可以用来显示或隐藏违规,这取决于其严重程度。 在运行 DRC 后,可以使用保存按钮创建一个纯文本格式的报告文件。

每个违规行为都涉及 PCB 上的一个或多个对象。 在违规列表中,涉及的对象列在违规行为下面。 点击列表中的违规行为将移动 “PCB 编辑器” 的视图,使受影响的区域居中。 点击违规所涉及的对象之一将高亮显示该对象。

窗口底部的数字显示错误、警告和排除的数量。每种类型的违规行为都可以用各自的复选框从列表中过滤出来。点击 删除标记 将清除所有违规行为,直到再次运行 DRC。

可以在对话框中右键单击违规行为,以忽略它们或改变其严重程度:

-

排除此违规行为: 忽略此特定的违规行为,但不影响任何其他违规行为。

-

更改严重程度: 将一个违规类型从警告改为错误,或将错误改为警告。这影响到一个给定类型的所有违规行为。

-

忽略所有: 忽略所有给定类型的违规。这个测试现在将出现在 忽略的测试 标签,而不是 违规 标签。

在设计规则检查器运行期间,排除的和忽略的违规行为会被记住。

间隙和约束解析

间隙和约束解析工具允许你检查哪些间隙和设计约束规则应用于选定的项目。 当设计具有复杂设计规则的 PCB 时,这些工具可以提供帮助,因为在这种情况下并不总是清楚哪些规则适用于哪些对象。

要检查两个对象之间适用的间隙规则,选择这两个对象并从 检查 菜单中选择 间隙解析。 间隙报告对话框将显示每个铜层上的对象之间所需的间隙,以及产生该间隙的设计规则。

要检查适用于单一对象的设计约束,选择它并从 检查 菜单中选择 约束解析。 约束报告对话框将显示适用于该对象的所有约束。

DRC configuration

The severity of each DRC check can be configured in the Violation Severity section of the Board Setup dialog. Each rule may be set to create an error marker, a warning marker, or no marker (ignored).

| 在设计规则检查器中可能会忽略个别规则违规。 在违规程度部分中将规则设置为忽略将完全禁用相应的设计规则检查。 请谨慎使用此设置。 |

List of DRC checks

The table below lists the design rules that KiCad checks and the default violation severity for each check. All severities are configurable. Some design are only available through custom design rules.

Electrical DRC checks

These DRC checks look for gross electrical issues on the board such as shorts and clearance violations.

| Violation | Description | Default Severity |

|---|---|---|

Items shorting two nets |

This violation occurs when copper items on different nets collide with each other. If this is intentional, consider using a net tie. |

Error |

Tracks crossing |

This violation occurs when tracks with different nets cross each other. |

Error |

Clearance violation |

This violation occurs when the distance between two copper items with different nets is smaller than the configured clearance for those nets. The allowed clearance between two items can come from the board-level minimum clearance, the net class settings for each net, or from custom rules. To see detailed information about the configured and actual clearances between two selected items, run the clearance resolution tool. This violation is also reported when the distance between two items is smaller than the configured physical clearance for those two items. Physical clearance constraints are not configured by default; see the custom rule documentation for how to configure physical clearance. |

Error |

Via is not connected or is connected on only one layer |

This violation occurs when a via is connected to copper objects on only one layer or is not connected to anything. As vias are intended to connect copper objects on different layers, this may indicate that an intended connection is missing. |

Warning |

Track has unconnected end |

This violation occurs when the end of a track segment is not connected to another copper object, such as another track segment, a via or pad, or a zone or copper graphical shape. |

Warning |

Thermal relief connection to zone incomplete |

This violation occurs when a pad’s connection to a zone does not have enough connected thermal relief spokes. The minimum allowed number of spokes can come from the board-level minimum thermal relief spoke count or can be configured with more granularity using custom rules. This check counts automatically generated spokes as well as manually drawn connections, so if the pad and zone geometry prevent enough spokes from being generated, you can manually add additional connections using tracks between the pad and the zone. |

Error |

Design for manufacturing DRC checks

These DRC checks look for issues in the board that may cause manufacturing problems.

| Violation | Description | Default Severity |

|---|---|---|

Board edge clearance violation |

This violation occurs when the distance between a copper object and the

board edge is smaller than the configured copper to edge clearance for those

items. For the purposes of this check, oval holes (which are routed rather

than drilled) are counted as board edges in addition to any graphic items

on the The allowed edge clearance between two items can come from the board-level minimum copper to edge clearance or from custom rules. A negative edge clearance allows objects to overlap with the board edge. To see detailed information about the configured and actual edge clearances between two selected items, run the clearance resolution tool. |

Error |

Hole clearance violation |

This violation occurs when the distance between a hole (pad or via) and another copper object (pad, track, via, or zone) is smaller than the configured copper to hole clearance for those objects. Objects are only considered in this check if they have layers in common. The allowed hole clearance between two items can come from the board-level minimum copper to hole clearance or from custom rules. To see detailed information about the configured and actual hole clearances between two selected items, run the clearance resolution tool. This violation is also reported when the distance between a hole and another object is smaller than the configured physical hole clearance for those two items. Physical hole clearance constraints are not configured by default; see the custom rule documentation for how to configure physical hole clearance. |

Error |

Drilled hole too close to other hole |

This violation occurs when the distance between a drilled hole and another hole is smaller than the configured hole to hole clearance. Through vias, blind/buried vias, and through holes in pads are considered drilled holes because the holes are made with a physical drill bit, which can shift or be damaged if other holes (drilled or otherwise) are too close. Micro vias are not considered drilled holes because they are drilled using a laser, which is not affected by other nearby holes. At least one of the holes must be mechanically drilled in order to be considered in this check. Blind/buried vias are only considered in this check when they share layers with the other hole. Non-circular holes are not included in this check because they are routed rather than drilled. Routing is typically performed after holes are drilled and with a stronger tool. |

Error |

Drilled holes co-located |

This violation occurs when a drilled hole and another hole are in the exact same location. The same types of holes are considered in this check as for the "Drilled hole too close to other hole" check. |

Warning |

Track width |

This violation occurs when the width of a track is outside of the configured range. The allowed width for a track can come from the board-level minimum track width or from custom rules. Note that an optimal track width can be configured for each net class in the net class settings, which sets a track width for the interactive router to use, but it does not set a minimum and maximum track width. No DRC violations will be reported for net class track width settings unless a minimum and/or maximum are configured using custom rules. To see detailed information about the configured track width for a particular track, run the constraints resolution tool. |

Error |

Annular width |

This violation occurs when a pad or via’s annular width is outside of the configured range. Board-level minimum annular width can be configured in board setup constraints. Board-level maximum width, as well as more specific rules, can be configured using custom rules. |

Error |

Hole size out of range |

This violation occurs when a drilled hole’s diameter is outside of the configured range. This check represents the smallest hole that can be drilled, i.e. the smallest drill bit size the manufacturer will use. This check therefore includes through vias, blind/buried vias, and through holes in pads. Micro vias are not included in this check because they are made using a laser rather than a physical drill bit. Board-level minimum through hole size can be configured in board setup constraints. Board-level maximum hole size, as well as more specific rules, can be configured using custom rules. |

Error |

Micro via hole size out of range |

This violation occurs when a micro via’s hole diameter is outside of the configured range. This check represents the smallest hole that can be laser drilled and therefore only applies to micro vias. Board-level minimum micro via hole size can be configured in board setup constraints. Board-level maximum hole size, as well as more specific rules, can be configured using custom rules. |

Error |

Courtyards overlap |

This violation occurs when a footprint’s courtyard overlaps with another

footprint’s courtyard. A nonzero clearance between two courtyards can be

configured using a |

Error |

Footprint has no courtyard defined |

This violation occurs when a footprint does not contain any graphic

shapes on its |

Ignore |

Footprint has malformed courtyard |

This violation occurs when a footprint has a courtyard containing non-closed shapes. Courtyards may contain multiple unconnected shapes without being considered malformed, as long as each shape is individually closed. |

Error |

Board has malformed outline |

This violation occurs when the shapes on the |

Error |

Copper sliver |

This violation occurs when small, wedge-shaped protrusions of copper are detected. These slivers can cause manufacturing, reliability, or electrical issues. |

Warning |

Solder mask aperture bridges items with different nets |

This violation occurs when a single opening in the soldermask exposes multiple copper items with different nets. This can result in solder shorting the two copper items during assembly. |

Error |

Copper connection too narrow |

This violation occurs when a copper connection necks down to a width that is narrower than the configured minimum connection width. The minimum connection width setting can come from the board-level minimum connection width or can be configured with more granularity using custom rules. |

Warning |

Schematic parity DRC checks

These DRC checks look for differences between the schematic and the board.

| Violation | Description | Default Severity |

|---|---|---|

Duplicate footprints |

This violation occurs when the board contains multiple footprints with the same reference designator are in the board. It is not reported if the footprints do not correspond to schematic symbols, however (if the footprints only exist in the board). |

Warning |

Missing footprint |

This violation occurs when a footprint is not in the board but is expected based on a corresponding symbol in the schematic. |

Warning |

Extra footprint |

This violation occurs when a footprint is in the board without a corresponding symbol in the schematic. |

Warning |

Footprint attributes don’t match symbol |

This violation occurs when a footprint’s Typically this is fixed by performing an Update PCB from Schematic or Update Schematic from PCB action to sync the fields and attributes, depending on whether the symbol or footprint, respectively, is correct. |

Warning |

Pad net doesn’t match schematic |

This violation occurs when a net does not match between a footprint pad and the corresponding symbol pin. This can be because the symbol pin’s net is different than the footprint pad’s net, because the footprint pad does not have a corresponding symbol pin, or because the symbol pin does not have a corresponding footprint pad. |

Warning |

Missing connection between items |

This violation occurs when two copper objects with the same net are not connected on the board. |

Error |

Signal integrity DRC checks

These DRC checks look for signal integrity issues in the board.

| Violation | Description | Default Severity |

|---|---|---|

Trace length out of range |

This violation occurs when a trace in a differential pair is too long or too

short compared to the configured minimum and maximum length for that trace.

The allowable trace length for different traces can be configured using the

|

Error |

Skew between traces out of range |

This violation occurs when the difference between the length of a trace and the average length of all traces being considered is longer than the configured maximum skew for that set of traces. For calculating the skew of a differential pair (two traces), the skew therefore is calculated as half the length difference between traces. The allowable maximum skew for a set of traces can be configured using the

|

Error |

Too many or too few vias on a connection |

This violation occurs when the number of vias assigned to a net is too low

or too high compared to the configured minimum and maximum for that net. The

allowable via count for different nets can be configured using the

|

Error |

Differential pair gap out of range |

This violation occurs when the gap between the two traces in a differential pair is too small or too large compared to the configured minimum and maximum for that differential pair. The gap is only checked on coupled (i.e. parallel) portions of the differential pair. The minimum and maximum allowable gap for a differential pair can be

configured using the Note that an optimal differential pair gap can be configured for each net class in the net class settings, which sets a gap for the differential pair router to use, but it does not set a minimum and maximum gap. No DRC violations will be reported unless a minimum and/or maximum are configured using custom rules. |

Error |

Differential uncoupled length too long |

This violation occurs when the portion of a differential pair that is uncoupled is longer than the configured maximum. A differential pair is considered uncoupled when its tracks are not parallel, for example when fanning out from a footprint. The maximum allowable uncoupled length for a differential pair can be

configured using the |

Error |

Readability DRC checks

These DRC checks look for issues that may affect legibility of text and other silkscreen objects on the board.

| Violation | Description | Default Severity |

|---|---|---|

Silkscreen overlap |

This violation occurs when a silkscreen object intersects another silkscreen object, which may affect readability. This check does not apply to silkscreen objects within the same footprint. The allowable distance between silkscreen objects can also be set to a nonzero number to enforce a silk to silk clearance using the board-level silkscreen minimum item clearance or using custom rules. A negative silkscreen clearance allows silkscreen to intersect other objects. |

Warning |

Silkscreen clipped by solder mask |

This violation occurs when a silkscreen object intersects a solder mask opening. This may result in silkscreen printed on bare copper or substrate. Board manufacturers may also discard any silkscreen that does not have solder mask underneath. Such outcomes could affect board assembly as well as silkscreen durability and readability. |

Warning |

Silkscreen clipped by board edge |

This violation occurs when a silkscreen object intersects a board edge, meaning that part of the silkscreen is outside of the board area. The allowable distance between silkscreen and the board edge can also be set to a nonzero number to enforce a clearance to the board edge using the board-level silkscreen minimum item clearance or using custom rules. A negative silkscreen clearance allows silkscreen to intersect other objects. |

Warning |

Text height out of range |

This violation occurs when a text object’s text height is outside of the configured range. Board-level minimum text height can be configured in board setup constraints. Board-level maximum height, as well as more specific rules, can be configured using custom rules. |

Warning |

Text thickness out of range |

This violation occurs when a text object’s text thickness is outside of the configured range. For the built-in KiCad stroke font, the thickness is the text thickness setting in the text object’s properties. For external fonts, this is the minimum physical thickness of all glyphs in the text object; this depends on the font geometry in combination with the font size, bold, and italic settings. Board-level minimum text thickness can be configured in board setup constraints. Board-level maximum thickness, as well as more specific rules, can be configured using custom rules. |

Warning |

Miscellaneous DRC checks

These DRC checks look for other miscellaneous issues in the board.

| Violation | Description | Default Severity |

|---|---|---|

Items not allowed |

This violation occurs when objects are placed in a location where they are

not allowed. This can be due to a rule area with a keep

out rule for the object’s type or due to a |

Error |

Copper zones intersect |

This violation occurs when copper zones with different nets collide with each other, shorting the two nets. |

Error |

Isolated copper fill |

This violation occurs when part of a copper fill is not connected to any other copper items with the same net. This is also referred to as an island. |

Warning |

Footprint is not valid |

This violation occurs when a footprint’s net tie group contains a pad that doesn’t exist in the footprint, or when a pad is in more than one net tie group. |

Error |

Padstack is questionable |

This violation occurs when a footprint pad has unusual settings that are probably a mistake. The settings that are checked are:

|

Warning |

PTH inside courtyard |

This violation occurs if a footprint’s plated through hole pad is within the courtyard of another footprint. |

Warning |

NPTH inside courtyard |

This violation occurs if a footprint’s nonplated through hole pad is within the courtyard of another footprint. |

Warning |

Item on a disabled copper layer |

This violation occurs if an item, for example a pad or via, is on a copper layer that does not exist in the board stackup. |

Error |

Unresolved text variable |

This violation occurs when a text variable in the board design or drawing sheet does not resolve (there is no defined value for the variable). |

Error |

Footprint component type doesn’t match footprint pads |

This violation occurs when a footprint’s component type (SMD, through hole, or unspecified) doesn’t match the expected type based on the footprint’s pads. If a footprint contains any through hole pads, it is expected to have the through hole component type. If it contains SMD pads and no through hole pads, its component type is expected to be SMD. If a footprint’s component type is unspecified, the footprint is not compared against its pads. |

Ignore |

Footprint not found in libraries |

This violation occurs when a footprint in the board is not in an active library in the global library table or the project-specific library table. This can be because the footprint’s library does not contain the footprint, the footprint’s library is not listed in either library table, or because the library is listed in a table but is disabled. As a consequence, you will not be able to update the footprint from the library or compare changes between the board and library versions of the footprint. |

Warning |

Footprint doesn’t match copy in library |

This violation occurs when a footprint in the board is different than the library version of the footprint. You can compare between the board and library versions of the footprint using the Compare Footprint with Library tool. If desired, you can update the board footprint to match the library footprint. |

Warning |

Through hole pad has no hole |

This violation occurs when a through hole footprint pad does not have a hole. |

Error |

DRC report file

An DRC report file can be generated and saved by clicking the Save… button in the DRC dialog. The file extension for DRC report files is .rpt. An example DRC report file is given below.

** Drc report for pic_programmer.kicad_pcb **

** Created on 2024-11-02T15:54:52-0400 **

** Found 4 DRC violations **

[starved_thermal]: Thermal relief connection to zone incomplete (layer bottom_layer; 1 spokes connected to isolated island)

Local override; error

@(223.5200 mm, 138.4300 mm): Zone [GND] on bottom_layer

@(175.2600 mm, 68.5800 mm): PTH pad 8 [GND] of P3

[starved_thermal]: Thermal relief connection to zone incomplete (layer bottom_layer; zone min spoke count 2; actual 1)

Local override; error

@(223.5200 mm, 138.4300 mm): Zone [GND] on bottom_layer

@(207.8990 mm, 118.1100 mm): PTH pad 5 [GND] of U5

[starved_thermal]: Thermal relief connection to zone incomplete (layer bottom_layer; 1 spokes connected to isolated island)

Local override; error

@(223.5200 mm, 138.4300 mm): Zone [GND] on bottom_layer

@(125.7300 mm, 111.7600 mm): PTH pad 10 [GND] of U2

[starved_thermal]: Thermal relief connection to zone incomplete (layer bottom_layer; zone min spoke count 2; actual 1)

Local override; error

@(223.5200 mm, 138.4300 mm): Zone [GND] on bottom_layer

@(118.1100 mm, 111.7600 mm): PTH pad 13 [GND] of U2

** Found 0 unconnected pads **

** Found 0 Footprint errors **

** End of Report **

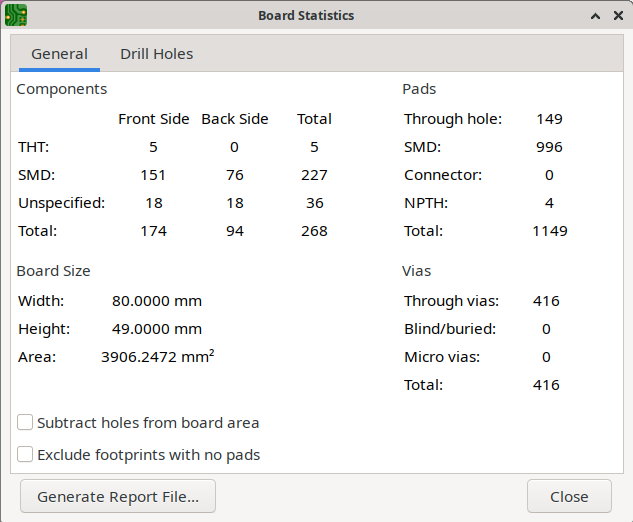

Board Statistics

The Board Statistics dialog shows a summary of the board’s contents, including the number of components, pads and vias; each by their own types as well as the overall board size.

测量工具

测量工具允许你在 PCB 上的各点之间进行距离和角度测量。 要激活该工具,请点击右侧工具栏的 ![]() 图标,或使用快捷键 Ctrl+Shift+M。 一旦该工具被激活,点击一次以设置测量起点,然后再点击一次以完成测量。

图标,或使用快捷键 Ctrl+Shift+M。 一旦该工具被激活,点击一次以设置测量起点,然后再点击一次以完成测量。

| 测量工具用于不需要永久显示的快速测量。 您所做的任何测量都将仅在该工具处于活动状态时显示。 要创建将显示在打印输出和打印中的永久性尺寸标注,请使用尺寸标注工具。 |

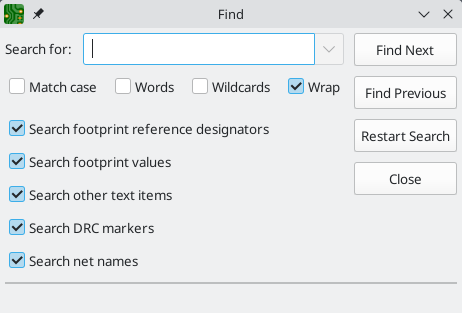

查找工具

查找工具在 PCB 中搜索文本,包括位号、封装字段和图形文本。当该工具找到一个匹配的文本时,画布会被放大,并将其置于匹配文本的中心位置,同时文本被高亮显示。使用顶部工具栏中的(![]() )按钮启动该工具。

)按钮启动该工具。

查找工具有几个选项:

匹配大小写: 选择搜索是否对大小写敏感。

关键词: 当选择时,搜索将只与 PCB 中的完整单词相匹配。当未选择时,如果搜索词是 PCB 中一个较长的词的一部分,搜索将匹配。

通配符: 当选择时,通配符可以在搜索词中使用。? 匹配任何单个字符,* 匹配任何数量的字符。请注意,当选择这个选项时,不会返回部分匹配结果:搜索 abc* 将匹配字符串 abcd,但搜索 abc 则不会。

Wrap: 选中时,搜索结果将在到达最后一个匹配项后返回到第一个匹配项。

搜索封装位号: 选择搜索是否应适用于封装位号。

搜索封装值: 选择搜索是否应适用于封装值字段。

搜索其他文本项目: 选择搜索是否应适用于其他文本项目,包括图形文本以及除了值和位号之外的封装字段。

搜索 DRC 标记: 选择搜索是否应适用于电路板上显示的 DRC 标记的违规描述。

Search net names: Selects whether the search should apply to the names of nets in the board.

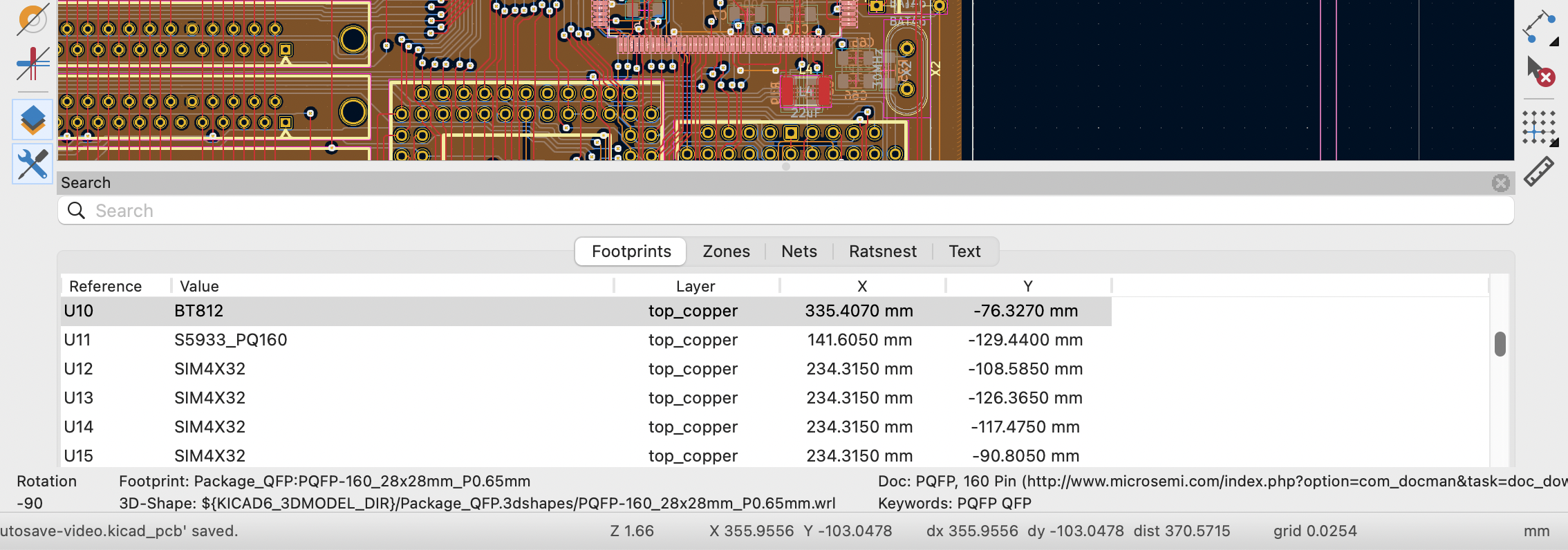

搜索面板

The search panel is a docked panel that lists information about footprints, zones, nets, ratsnest lines (unrouted segments), and text from the PCB. You can optionally filter the list based on a search string. When no filter is used, all items in the design are listed in the corresponding tab.

Items are filtered based on their properties: footprints are filtered by their reference designator and value, zones by the zone name, net and ratsnest items by the net name, and text (text, textboxes, and dimensions) by the text content. You can sort the filtered results in ascending or descending order of the value in a particular column by clicking on that column header.

Filters support wildcards: * matches any characters, and ? matches any single character. You can also use regular expressions, such as /footprint value/.

The displayed information depends on the item type. In addition to the item’s name and/or value, physical items (footprints, zones, and text) list their layer and X/Y location. Text also displays the type of text object (text, textbox, or dimension.) Net and ratsnest items list their net name and net class.

When you click an item in the search panel, the item is selected in the editing canvas. Double-clicking an item in the search panel opens its properties dialog (for net and ratsnest items, the net classes dialog is opened instead).

Show or hide the search panel with View → Show Search Panel or use the Ctrl+G shortcut.

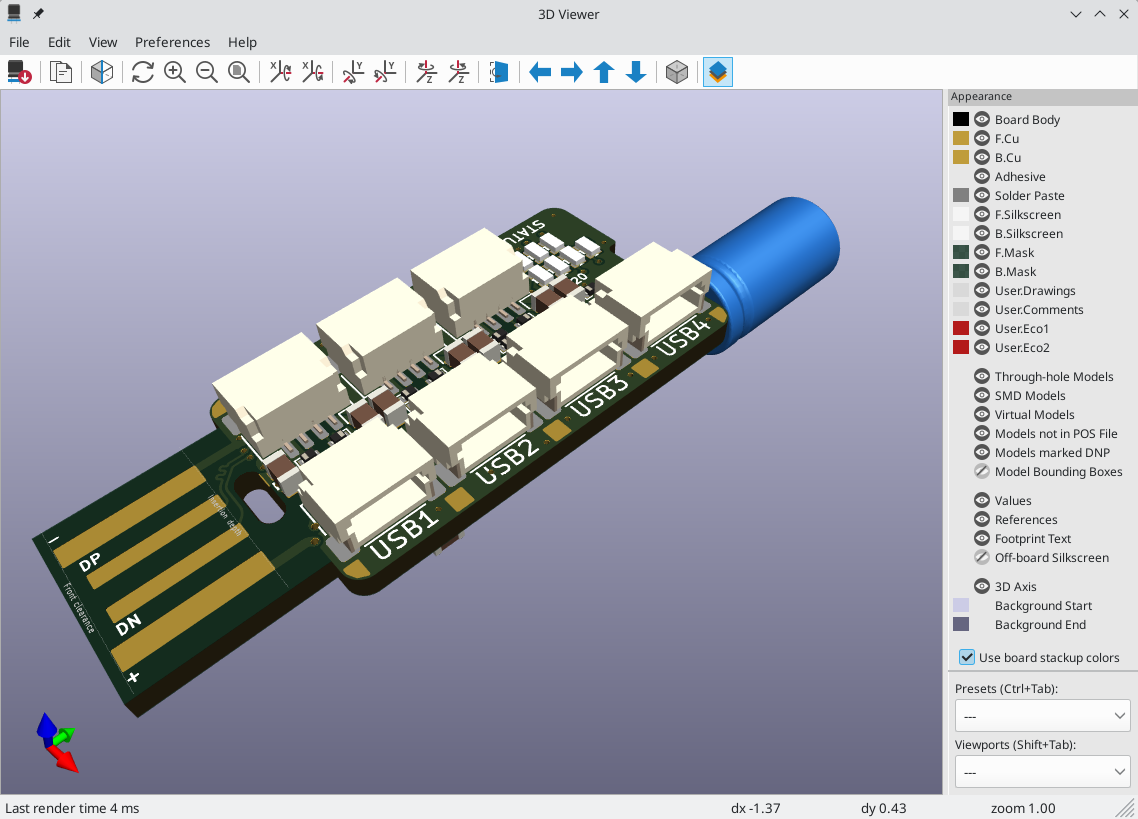

3D 查看器

The 3D Viewer shows a 3-dimensional view of the board and the components on the board. You can view the board from different perspectives, show or hide different types of components, cross-probe from the PCB Editor to the 3D viewer, and generate raytraced renders of the board. Show the 3D Viewer with View → 3D Viewer or use the Alt+3 shortcut.

| 仅当 3D 模型文件存在并且已被 分配到封装 时,元件的 3D 模型才会出现。 |

| KiCad 标准库中的许多封装还没有为它们创建模型文件。然而,这些封装可能包含一个指向尚不存在的 3D 模型的路径,以期待将来创建 3D 模型。 |

浏览 3D 视图

用鼠标左键拖动将旋转 3D 视图。 默认情况下,这是电路板的中心,但可以通过将光标移动到所需点上并按 Space 将轴心点重置为电路板上的新点。 滚动鼠标滚轮将放大或缩小视图。 按住 Ctrl 滚动可左右平移视图,按住 Shift 滚动可上下平移视图。 使用鼠标中键拖动也可以平移视图。

Different sized 3D grids can be set using the View → 3D Grid menu. Bounding boxes for each component can be enabled with Preferences → Show Model Bounding Boxes.

当 PCB 编辑器和 3D 查看器同时打开时,在 PCB 编辑器中选择一个封装也会在 3D 查看器中高亮显示该元件。高亮显示的颜色可以在 偏好设置 → 偏好设置… → 3D 查看器 → 实时渲染器 → 选择颜色 中调整。

Appearance Manager

The Appearance Manager is a panel at the right of the viewer which provides controls to manage the visibility, color, and opacity of different types of objects and board layers in the 3D view.

Each layer or type of object in the list can be individually shown or hidden by clicking its corresponding visibility icon. PCB layers can have their colors customized; double-click on the color swatch next to the item type to edit the item’s color and opacity. To use the colors selected in the Board Setup dialog’s Physical Stackup editor, enable the use board stackup colors option.

You can save an appearance configuration as a preset, or load a configuration from a preset, using the Preset selector at the bottom. The Ctrl+Tab hotkey cycles through presets; press Tab repeatedly while holding Ctrl to cycle through multiple presets. Several built-in presets are available: "Follow PCB Editor" matches the visibility settings in the PCB editor, "Follow PCB Plot Settings" matches the visibility settings selected in the Plot dialog, and "legacy colors" matches the default 3D Viewer color settings from older versions of KiCad.

Finally, you can save a viewport for later retrieval using the Viewports selector at the bottom. You can quickly cycle between saved viewports using Shift+Tab; pressing Tab repeatedly while holding Shift will cycle through multiple viewports.

用 3D 查看器生成图像

当前的 3D 视图可以用 文件 → 将当前视图导出为 PNG… 或 将当前视图导出为 JPG…,根据所需的图像格式,将其保存为一个图像。也可以用 ![]() 按钮,或 编辑 → 复制 3D 图像 将当前视图复制到剪贴板上。

按钮,或 编辑 → 复制 3D 图像 将当前视图复制到剪贴板上。

3D 查看器有一个光线跟踪渲染模式,它使用比默认渲染模式更精确的物理渲染模型来显示电路板。 光线追踪比默认渲染模式慢,但当需要最吸引人的视觉效果时,可以使用它。使用 ![]() 按钮,或者使用 偏好设置→光线追踪 来启用光线追踪模式。在光线追踪模式下,3D 网格和选择高亮不会显示。

按钮,或者使用 偏好设置→光线追踪 来启用光线追踪模式。在光线追踪模式下,3D 网格和选择高亮不会显示。

颜色和其他渲染选项,包括光线跟踪和非光线跟踪模式,都可以在 偏好设置 → 偏好设置… → 3D查看器 中调整。

3D 查看器控制

许多查看选项是通过顶部的工具栏控制的。

|

Reload the 3D model |

|

Copy 3D image to clipboard |

|

Render current view using raytracing |

|

Redraw |

|

Zoom in |

|

Zoom out |

|

Fit drawing in display area |

|

Rotate X clockwise |

|

Rotate X counterclockwise |

|

Rotate Y clockwise |

|

Rotate Y counterclockwise |

|

Rotate Z clockwise |

|

Rotate Z counterclockwise |

|

Flip board view |

|

Pan board left |

|

Pan board right |

|

Pan board up |

|

Pan board down |

|

Enable/disable orthographic projection |

|

Show/hide the Appearance Manager |

网络检查

The Net Inspector allows you to view statistics about all the nets in a board. To open the inspector, click the ![]() icon at the top of the Nets section of the Appearance panel, or select Net Inspector from the Inspect menu.

icon at the top of the Nets section of the Appearance panel, or select Net Inspector from the Inspect menu.

点击网络列表中的一个网络会在电路板上高亮显示该网络。 单击列标题允许您按该列对网络列表进行排序。

The Group By field allows you to combine different nets together and view the total length of the combined nets. For example, if you have two nets named DATA0 and DATA0_EXT, using a Group By value of DATA0* will create a group containing both nets. More complicated groupings can be created by changing the Group By mode from Wildcard to RegEx (regular expressions). The substring (Substr) variants of the Group By mode will create groups for each set of nets that matches the pattern differently.

例如,如果您有 U1D+,U1D-,U2D+ 和 U2D-,分组模式 U*D 将在通配符模式下匹配所有四个网络,创建一个单一的组 U*D。 在通配符子串模式下,它将匹配所有四个网络,但创建两个不同的组:U1D 和 U2D。

焊盘计数 和 过孔计数 显示一个网络的焊盘(表面贴装和通孔)及过孔的数量。 过孔长度 显示每个过孔的总高度(不考虑过孔连接到哪个铜层)。 换句话说,过孔长度等于过孔数乘以电路板的层叠高度。 布线长度 显示一个网络中所有布线的总长度,不考虑拓扑结构。 晶圆长度 显示了网络中所有焊盘设置的 “晶圆到焊盘长度“ 值的总和。

Differences between Net Inspector and Length Tuner

The Net Inspector may report different net lengths than the length tuner, because the two tools have different purposes and calculate track/net lengths differently. In short, the Net Inspector sums up the total length of each track segment and via on a net, while the length tuner calculates the effective electrical length of a path between two points on a net. The specific differences are as follows:

-

The Net Inspector reports track length as a simple sum of the length of each track segment on a net. The length tuner calculates an effective electrical length of a net, which includes optimizing paths through pads to calculate the shortest possible path.

-

If a routed net has a branching topology, the Net Inspector total includes the length of each branch in the total. The length tuner calculates a point-to-point length; if there are any branches, the length tuner will stop at the closest branch and report the length up to the branch.

-

The Net Inspector always includes the effective via height in its via length and total length calculations. If a via connects to traces on both the top and bottom layers, the full via height is included in the length calculation. Otherwise, only the stackup height between the connected layers is included. The length tuner calculates effective via height in the same way as the Net Inspector, but via height is only included in the length calculation when the use stackup height setting is enabled board constraint settings. If the setting is disabled, the length tuner will not include vias in its calculations at all.